Хосолмол метал-оксид-хагас дамжуулагч (Complementary Metal Oxide Semiconductor - CMOS) бүлийн логик гейтүүд нь N ба P сувагтай MOSFET тарзисторыг 2-уланг ашигладаг. Үндсэн давуу тал нь маш бага чадал зарцуулдаг. Энэ нь нэг чип дээр маш олон тооны CMOS гейтүүдийг байрлуулах боломжийг олгодогоороо биполяр болон NMOS технолгиос ялгаатай. CMOS технологи нь өнөөдөр хагас дамжуулагчийн технологи дотроо микропроцессор, микроконтроллер, санах ойн төхөөрөмж, хэрэглээний тусгай интегралчлагдсан хэлхээ (ASIC) зэргийг үйлдвэрлэхэд давамгайлах байр суурьтай байна. CMOS интегралчлагч хэлхээ нь дотроо 4000A, 4000B, 4000UB, 74C, 74HC, 74HCT, 74AC, 74ACT гэсэн дэд бүлүүдэд хуваагдана.

CMOS элементийн логик хүчдлийн төвшинг 5.1-р зурагт үзүүлэв.

Зураг 5.1. CMOS логик хүчдлийн төвшин

CMOS элементийн ашиглах тэжээлийн хүчдэл нь 3-18в-ын хооронд нэлээд өргөн мужийг ашигладагаараа ТТЛ элементээс ялгаатай. Өөрөөр хэлбэл ТТЛ элементийн хувьд +5в-ийг логик 1 гэж үздэг байсан бол CMOS элементийн хувьд логик 1-д харгалзах хүчдлийн төвшин нь 3-10в хооронд байж болно гэсэн үг.

Бид энэ хэсэгт CMOS технологийг ашиглан үндсэн логик үйлдлүүд болох инвертер, NAND, NOR, AND, OR, XOR, XNOR, AND-OR-invert, OR-AND-invert үйлдлүүдийг хэрхэн гүйцэтгэдэг болохыг үзнэ.

CMOS инвертер бол CMOS технологийн үндсэн суурь элемент болно. CMOS инвертерийг N-сувагтай болон P-сувагтай MOSFET транзисторуудыг 5.2-р зурагт үзүүлсний дагуу цуваагаар холбож хийнэ.

Зураг 5.2. CMOS инвертер

Хүснэгт 5.1

A | Gate 1 | Q1 | Gate2 | Q2 | Y |

0 | 0 | ON | 0 | OFF | 1 |

1 | 1 | OFF | 1 | ON | 0 |

Хэрэв оролт логик 1 төлөвт байвал Р-сувагтай MOSFET транзистор болох Q1 транзистор хэрчилтийн төлөвт буюу хаалттай, N-сувагтай MOSFET транзистор болох Q2 транзистор ханалтын төлөвт буюу нээлттэй байна. Q2 ханалтын төлөвт байх тул гаралт бараг газартай адилхан буюу логик 0 төлөвт байна.

Хэрэв оролт логик 0 төлөвт байвал Р-сувагтай MOSFET транзистор болох Q1 транзистор ханалтын төлөвт буюу нээлттэй, N-сувагтай MOSFET транзистор болох Q2 транзистор хэрчилтийн төлөвт буюу хаалттай байна. Q1 ханалтын төлөвт байх тул гаралт бараг тэжээлтэй адилхан буюу логик 1 төлөвт байна.

Хэрэв оролт логик 0 ба 1-ийн аль нь ч биш сул орхигдсон байвал (хөвөгч оролттой байвал) 2 транзистор зэрэг нээгдэж богино холболт бүхий хэлхээ үүсэх боломжтой тул оролтыг юунд ч холбохгүй сул орхихыг хориглоно.

Зураг 5.1-ээс тэжээл болон газрын хооронд шууд гүйдэл гүйх боломжгүйн харагдаж байна. Өөрөөр хэлбэл 2 транзисторын аль нэг нь нээлттэй байхад үлдсэн нь хаалттай байна. 2-ул зэрэг гүйдэл дамжуулах буюу тэжээлээс шууд газар луу гүйдэл гүйх боломж хөвөгч оролттой үед л боломжтой учраас үүнийг хориглоно. Учир нь 2 транзистор 2-ул нээлттэй үед тэдгээрийн эсэргүүцэл маш бага байдаг тул транзисторуудаар хэт их гүйдэл гүйж тэдгээрийг гэмтээдэг.

CMOS инвертерийг харахад 2 транзистораас тогтох ба гаралтын аль нэг төлөвт эдгээр транзисторын аль нэг нь хаалттай байх тул чадлыг сарниулахгүй. Зөвхөн гейтэд байх метал-оксид-хагас дамжуулагч бүтэцтэй МОХ конденсатор цэнэглэгдэж цэнэгээ алдах хугацаанд чадал сарниулна. Энэ чадлын хэмжээ түлхүүрийн горимын давтамжаас шууд хамаарна. Өөрөөр оролтын логик 1 ба логик 0 төлөв хэр өндөр давтамжтайгаар өөрчлөгдөнө төдийчинээ их чадлыг сарниулна.

5.3-ийн зурагт 2 оролттой CMOS NAND гейтийг үзүүлэв.

Зураг 5.3. CMOS NAND гейт

Хүснэгт 5.2

A | B | Gate1 | Q1 | Gate2 | Q2 | Gate3 | Q3 | Gate4 | Q4 | Y |

0 | 0 | 0 | ON | 0 | ON | 0 | OFF | 0 | OFF | 1 |

0 | 1 | 1 | OFF | 0 | ON | 0 | OFF | 1 | ON | 1 |

1 | 0 | 0 | ON | 1 | OFF | 1 | ON | 0 | OFF | 1 |

1 | 1 | 1 | OFF | 1 | OFF | 1 | ON | 1 | ON | 0 |

Зургаас харахад P-сувагтай MOSFET транзисторууд болох Q1 ба Q2-ийг тэжээлтэй зэрэгцээ, N-сувагтай MOSFET транзисторууд болох Q3 ба Q4-ийг газартай цуваа холбосон байна.

Хэрэв гаралтыг логик 0 төлөвт байлгахын тулд Q3 ба Q4 транзисторууд зэрэг нээлттэй, Q1 ба Q2 транзисторууд зэрэг хаалттай байх шаардлагатай байна. Энэ нь оролтууд адилхан 2-ул логик 1 гэсэн төлөвт байхад л боломжтой.

Хэрэв гаралтыг логик 1 төлөвт байлгахын тулд Q3 ба Q4 транзисторууд аль нэг нь хаалттай эсвэл 2-ул зэрэг хаалттай, Q1 ба Q2 транзисторууд аль нэг нь нээлттэй эсвэл 2-ул зэрэг нээлттэй байх шаардлагатай. Энэ нь 2 оролтын аль нэг нь логик 0, эсвэл 2-ул зэрэг логик 0 гэсэн төлөвт байхад л боломжтой.

5.4-ийн зурагт 2 оролттой CMOS NOR гейтийг үзүүлэв.

Зураг 5.4. CMOS NOR гейт

Хүснэгт 5.3

A | B | Gate1 | Q1 | Gate2 | Q2 | Gate3 | Q3 | Gate4 | Q4 | Y |

0 | 0 | 0 | ON | 0 | ON | 0 | OFF | 0 | OFF | 1 |

0 | 1 | 0 | ON | 1 | OFF | 0 | OFF | 1 | ON | 0 |

1 | 0 | 1 | OFF | 0 | ON | 1 | ON | 0 | OFF | 0 |

1 | 1 | 1 | OFF | 1 | OFF | 1 | ON | 1 | ON | 0 |

Зургаас харахад P-сувагтай MOSFET транзисторууд болох Q1 ба Q2-ийг тэжээлтэй цуваа, N-сувагтай MOSFET транзисторууд болох Q3 ба Q4-ийг газартай зэрэгцээ холбосон байна.

Хэрэв гаралтыг логик 1 төлөвт байлгахын тулд Q3 ба Q4 транзисторууд зэрэг хаалттай, Q1 ба Q2 транзисторууд зэрэг нээлттэй байх шаардлагатай байна. Энэ нь оролтууд адилхан 2-ул логик 0 гэсэн төлөвт байхад л боломжтой.

Хэрэв гаралтыг логик 0 төлөвт байлгахын тулд Q3 ба Q4 транзисторууд аль нэг нь нээлттэй эсвэл 2-ул зэрэг нээлттэй, Q1 ба Q2 транзисторууд аль нэг нь хаалттай эсвэл 2-ул зэрэг хаалттай байх шаардлагатай. Энэ нь 2 оролтын аль нэг нь логик 1, эсвэл 2-ул зэрэг логик 1 гэсэн төлөвт байхад л боломжтой.

5.5-р зурагт 2 оролттой CMOS AND гейтийг үзүүлэв.

Зураг 5.5. CMOS AND гейт

Хүснэгт 5.4

A | B | Q1 | Q2 | Q3 | Q4 | C | Q5 | Q6 | Y |

0 | 0 | ON | ON | OFF | OFF | 1 | OFF | ON | 0 |

0 | 1 | ON | OFF | OFF | ON | 1 | OFF | ON | 0 |

1 | 0 | OFF | ON | ON | OFF | 1 | OFF | ON | 0 |

1 | 1 | OFF | OFF | ON | ON | 0 | ON | OFF | 1 |

Зургаас харахад NAND гейтийг инвертертэй цуваа холбох замаар AND гейтийг хийсэн байна.

5.6-р зурагт 2 оролттой CMOS OR гейтийг үзүүлэв.

Зураг 5.6. CMOS OR гейт

Хүснэгт 5.5

A | B | Q1 | Q2 | Q3 | Q4 | C | Q5 | Q6 | Y |

0 | 0 | ON | ON | OFF | OFF | 1 | OFF | ON | 0 |

0 | 1 | OFF | ON | OFF | ON | 0 | ON | OFF | 1 |

1 | 0 | ON | OFF | ON | OFF | 0 | ON | OFF | 1 |

1 | 1 | OFF | OFF | ON | ON | 0 | ON | OFF | 1 |

Зургаас харахад NOR гейтийг инвертертэй цуваа холбох замаар OR гейтийг хийсэн байна.

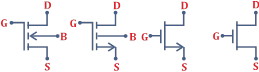

5.7-р зурагт N-сувагтай MOSFET транзисторыг дүрсэлсэн симболын хувилбаруудыг үзүүлэв. Энд эхний 2 хувилбарт Gate, Drain, Source их бие буюу Body гэсэн 4 хөлтэйгээр дүрсэлсэн бол сүүлийн 2 хувилбарт N-сувагтай MOSFET-ийг үндсэн 3 хөл болох Gate, Drain, Source гэсэн 3 хөлтэйгээр дүрсэлсэн болно. Эдгээрээс хамгийн сүүлийн симболыг цаашид ашиглах ба үүнийг N-суваг нь нэмэх хүчдлээр буюу логик 1 хүчдлээр үүсч транзисторыг нээн гэж ойлгоно.

Зураг 5.7. N-сувагтай MOSFET транзистор

5.8-р зурагт P-сувагтай MOSFET транзисторыг дүрсэлсэн симболыг үзүүлэв. Эдгээрээс хамгийн сүүлийн симболыг цаашид ашиглах ба үүнийг P-суваг нь 0 хүчдлээр буюу логик 0 хүчдлээр үүсч транзисторыг нээн гэж ойлгоно.

Зураг 5.8. P-сувагтай MOSFET транзистор

Инвертер, NAND, NOR, AND ба OR гейтүүдийг дүрсэлсэн байдлыг харахад CMOS логик хэлхээ нь Pull-up буюу татагч транзисторын хэлхээ, Pull-down буюу түлхэгч транзисторын хэлхээ хэмээх 2 хэлхээнээс тогтдог болохыг харж болно. (зураг 5.9)

Зураг 5.9. CMOS логик гейт

Татагч ба түлхэгч хэлхээ нь зэрэг нээлттэй байхгүй байх бөгөөд гаралт 1 үед татагч хэлхээ нээлттэй, гаралт 0 үед түлхэгч хэлхээ нээлттэй байна.

Татагч хэлхээ нээлттэй үед гаралт тэжээлтэй шууд холбоотой байх бөгөөд тулгуур гүйдэл тэжээлээс ачааллын оролт уруу гүйнэ. Өөрөөр хэлбэл татагч хэлхээ нь тулгуур гүйдлийн замыг тогтооно. Товчоор татагч хэлхээг гаралтыг дээш татаж шууд тэжээлтэй холбох зориулалттай хэлхээ гэж ойлгож болно.

Түлхэгч хэлхээ нээлттэй үед гаралт шууд газардуулагдсан байх бөгөөд ачааллын оролтоос ирэх живэгч гүйдэл шууд газардуулагдсан байна. Өөрөөр хэлбэл түлхэгч хэлхээ нь живэгч гүйдлийн замыг тогтооно. Товчоор түлхэгч хэлхээг гаралтыг доош түлхэж шууд газартай холбох зориулалттай хэлхээ гэж ойлгож болно.

Татагч ба түлхэгч хэлхээ зэрэг хаалттай бол тулгуур ба живэгч гүйдлийн зам тасарч хэлхээ нээлттэй хэлхээгээр солигдох тул энэ үед гаралтыг Z буюу high impedance гаралт гэнэ.

Татагч хэлхээний хувьд зөвхөн тулгуур гүйдлийн замыг тогтоох тул живэгч гүйдлийн зам тодорхойгүй байдаг. Харин түлхэгч хэлхээний хувьд зөвхөн живэгч гүйдлийн замыг тогтоох тул тулгуур гүйдлийн зам тодорхойгүй байдаг. Иймээс татагч ба түлхэгч хэлхээг 2-уланг байгуулснаар сая хэлхээ маань бүрэн төгс болно.

5.10-р зурагт татагч хэлхээний үндсэн 3 хувилбарыг үзүүлэв. Энд эхний хэлхээний 2 оролтын аль нэг нь 0 бол тухайн транзистор нээгдэж гаралтанд логик 1 байна. Дунд үзүүлсэн хэлхээний 2 оролт 2-ул 0 байж 2 транзистор зэрэг нээгдсэн тохиолдолд л гаралт логик 1 байна. Сүүлийн хэлхээний хувьд нэг бол А оролт 0 бол тухайн транзистор нээгдэж гаралт 1 болно, эсвэл B ба C оролт зэрэг 0 бол B ба C транзисторуудыг нээснээр гаралт 1 болно.

Зураг 5.10. Татагч хэлхээний үндсэн хувилбарууд

Тодорхой болгох үүднээс дээрх 3 хэлхээний үнэмшлийн хүснэгтийг байгуулья.

Хүснэгт 5.6

A | B | Y | A | B | Y | A | B | C | Y |

0 | 0 | 1 | 0 | 0 | 1 | 0 | X | X | 1 |

0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

Y=A’+B’ | Y=A’*B’ | 1 | 1 | 1 | 0 | ||||

Y=A’+B’*C’ | |||||||||

5.11-р зурагт түлхэгч хэлхээний үндсэн 3 хувилбарыг үзүүлэв. Энд эхний хэлхээний 2 оролтын аль нэг нь 1 бол тухайн транзистор нээгдэж гаралтанд логик 0 байна. Дунд үзүүлсэн хэлхээний 2 оролт 2-ул 1 байж 2 транзистор зэрэг нээгдсэн тохиолдолд л гаралт логик 0 байна. Сүүлийн хэлхээний хувьд нэг бол А оролт 1 бол тухайн транзистор нээгдэж гаралт 0 болно, эсвэл B ба C оролт зэрэг 1 бол B ба C транзисторуудыг нээснээр гаралт 0 буюу газартай адилхан болно.

Зураг 5.11. Түлхэгч хэлхээний үндсэн хувилбарууд

Тодорхой болгох үүднээс дээрх 3 хэлхээний үнэмшлийн хүснэгтийг байгуулья.

Хүснэгт 5.7

A | B | Y | A | B | Y | A | B | C | Y |

0 | 0 | 1 | 0 | 0 | 1 | 1 | X | X | 0 |

0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

Y=(A+B)’ | Y=(A*B)’ | 0 | 1 | 1 | 0 | ||||

Y=(A+B*C)’ | |||||||||

Одоо XOR гейтийг авч үзье. Үнэндээ XOR гейт нь Exclusive OR буюу онцгой OR гейтийн товчилсон тэмдэглэгээ юм. OR үйлдэл нь архиметикийн нэмэх үйлдэлтэй төсөөтэй тул түүнийг нэмэх тэмдгээр тэмдэглэдэг боловч 1 + 1 = 1 байдаг. Онцгой OR үйлдэл нь дээрх алдааг засч OR үйлдлийг нэмэх үйлдэлтэй илүү адилхан болгож өгсөн. Тиймээс онцгой OR үйлдлийг дугуй доторх нэмэх тэмдгээр тэмдэглэдэг. Ингээд онцгой OR үйлдлийг энгийн OR үйлдэлтэй харьцуулж үзье.

Хүснэгт 5.8

0 + 0 = 0 0 ⊕ 0 = 0 0 + 1 = 1 0 ⊕ 1 = 1 1 + 0 = 1 1 ⊕ 0 = 1 1 + 1 = 1 1 ⊕ 1 = 0 | 0 + 0 + 0 = 0 0 ⊕ 0 ⊕ 0 = 0 0 + 0 + 1 = 1 0 ⊕ 0 ⊕ 1 = 1 0 + 1 + 0 = 1 0 ⊕ 1 ⊕ 0 = 1 0 + 1 + 1 = 1 0 ⊕ 1 ⊕ 1 = 0 | 1 + 0 + 0 = 1 1 ⊕ 0 ⊕ 0 = 1 1 + 0 + 1 = 1 1 ⊕ 0 ⊕ 1 = 0 1 + 1 + 0 = 1 1 ⊕ 1 ⊕ 0 = 0 1 + 1 + 1 = 1 1 ⊕ 1 ⊕ 1 = 1 |

2 оролттой онцгой OR үйлдлийг илэрхийллийг ашиглан гүйцэтгэж болно.

Үүний тулд эхлээд түлхэгч хэлхээ буюу pull-down хэлхээг байгуулья. (зураг 5.12)

Зураг 5.12. XOR гейтийн түлхэгч хэлхээ

Дараа нь татагч хэлхээ буюу pull-up хэлхээг байгуулья. (зураг 5.13)

Зураг 5.13. XOR гейтийн татагч хэлхээ

Ингээд онцгой OR-ийн татагч ба түлхэгч хэлхээг ашиглан XOR CMOS гейтийг байгуулна. (зураг 5.14)

Зураг 5.14. XOR CMOS гейт

Exclusive NOR буюу онцгой NOR гейтийг авч үзье. 2 оролттой онцгой NOR үйлдлийг илэрхийллийг ашиглан гүйцэтгэж болно.

Үүний тулд эхлээд түлхэгч хэлхээ буюу pull-down хэлхээг байгуулья. (зураг 5.15)

Зураг 5.15. XNOR гейтийн түлхэгч хэлхээ

Дараа нь татагч хэлхээ буюу pull-up хэлхээг байгуулья. (зураг 5.16)

Зураг 5.16. XNOR гейтийн татагч хэлхээ

Ингээд онцгой NOR-ийн татагч ба түлхэгч хэлхээг ашиглан XNOR CMOS гейтийг байгуулна. (зураг 5.17)

Зураг 5.17. XNOR CMOS гейт

AND-OR-invert үйлдлийг CMOS технологийг ашиглан хэрхэн гүйцэтгэж болохыг авч үзье. AND-OR-invert үйлдлийн Булийн илэрхийлэл нь байна.

AND-OR-invert-ийн татагч ба түлхэгч хэлхээг 5.18-р зурагт үзүүлэв.

Зураг 5.18. AND-OR-invert-ийн татагч-түлхэгч хэлхээ

5.19-р зурагт AND-OR-invert-ийг үзүүлэв.

Зураг 5.19. AND-OR-invert

OR-AND-invert үйлдлийг CMOS технологи ашиглан хэрхэн гүйцэтгэхийг үзье. OR-AND-invert үйлдлийн Булийн илэрхийлэл нь байна. (зураг 5.20)

Зураг 5.20. OR-AND-invert

CMOS технологи нь дамжуулагч гейт буюу transmission gate (bilateral switch) гэж нэрлэгддэг тусгай гейтийг агуулдагаараа биполяр транзистор бүхий өмнө үзсэн технологиос онцлог шинжтэй болно. Энэ нь үнэндээ нэг туйл, нэг замтай (single-pole, single-throw буюу SPST switch) түлхүүр юм. Түлхүүрийн нээгдэх ба хаагдах үйлдлийг логик төвшингээр удирдах болно. Өөрөөр хэлбэл логик 0 төвшингээр дамжуулагч гейт нээгдэж, логик 1 төвшингөөр дамжуулагч гейт хаагдана. (зураг 5.21)

Зураг 5.21. Дамжуулагч гейт

Татагч-түлхэгч буюу totem-pole гаралттай элементийн гаралтыг хооронд нь шууд холбож болдоггүй талаар ТТЛ элементийг үзэх үед танилцсан. Иймээс уламжлалт CMOS элементүүдийн гаралтыг хооронд нь шууд холбож болохгүй. Харин нээлттэй-коллектор бүхий гаралттай буюу татагч хэлхээгүй гаралттай элементүүдийн гаралтыг шууд холбож татагч хэлхээг татагч резистор тавьж шийдэж болдог тухай үзсэн. Энэ нь шууд гаралтуудын хувьд AND, урвуу гаралтуудын хувьд OR үйлдлийг гүйцэтгэдэг сайн талтай.

Үүнтэй адилаар нээлттэй-драйн гаралттай CMOS-уудын хувьд гаралтуудыг нь хооронд шууд холбож, татагч хэлхээг нэг ширхэг татагч резистороор орлуулан хэрэглэж болно. (зураг 5.22)

Зураг 5.22. Нээлттэй-драйн гаралттай инвертер

Татагч-түлхэгч гаралт, нээлттэй-драйн гаралттай CMOS-уудаас гадна 3 төлөвт гаралттай CMOS-ууд өргөн хэрэглэгддэг. Өөрөөр хэлбэл уламжлалт CMOS хэлхээ нь татагч-түлхэгч хэлхээнээс тогтох ба татагч хэлхээ нээлттэй бол гаралтыг дээш татаж тэжээлтэй холбох тул тэжээлээс ачаалал уруу чиглэлтэй тулгуур гүйдэл гүйнэ. Харин түлхэгч хэлхээ нээлттэй бол гаралтыг доош түлхэж газартай холбох тул ачааллаас ирсэн живэгч гүйдэл газардуулагдана. Татагч ба түлхэгч хэлхээ зэрэг нээлттэй бол транзистораар хэт их гүйдэл гүйж тэдгээрийг гэмтээх боломжтой байдаг. Татагч-түлхэгч хэлхээнүүд зэрэг хаалттай бол тулгуур ба живэгч гүйдлийн аль алиных нь зам тасарч хэлхээ нээлттэй хэлхээгээр солигдох тул ийм гаралтыг хэт өндөр эсэргүүцэлтэй буюу high impedance гаралт гээд Z гэж тэмдэглэдэг.

5.23-р зурагт 3 төлөвт гаралттай CMOS буферыг үзүүлэв. Enable оролтыг идэвхжүүлбэл энгийн буфер болох ба Enable оролтыг идэвхжүүлээгүй тохиолдолд татагч ба түлхэгч транзисторууд зэрэг хаалттай болж хэлхээ тасарна. 3 төлөвт гаралттай CMOS элементийг 3 төлөвт гаралттай ТТЛ элементтэй адилхан олон төхөөрөмжүүд нэг баазыг хамтран ашиглаж байх үед аль төхөөрөмж тухайн агшинд баазыг ашиглахыг тогтоохонд хэрэглэнэ.

Зураг 5.23. 3 төлөвт гаралттай буфер

CMOS элементийн хэрэглээгүй оролтуудыг сул орхиж буюу хөвөгч хэвээр үлдээж хэрхэвч болохгүй. Хөвөгч оролт нь статик цэнэг хуримтлуулах нэг шалтгаан болдог. Үүнээс гадна татагч ба түлхэгч хэлхээний транзисторууд зэрэг дамжуулагч байх боломжийг олгож чадлын зарцуулалтыг ихэсгэж улмаар халалт өгдөг муу талтай. Ийм учраас хэрэглээгүй сул оролтуудыг хөвөгч хэвээр үлдээлгүйгээр газар болон тэжээлийн аль нэгд заавал холбож хэрэглэнэ.

CMOS элементүүд нь статик цэнэгт хэт мэдрэмтгий. Учир нь CMOS элементийн гейт нь металл-оксид-хагас дамжуулагч гэсэн бүтэцтэй конденсатор болно. Иймээс гейтэд хуримтлагдсан статик цэнэгээс хамаарч оксидын давхарга нэвт цохигдон гэмтэх магадлал өндөр байдаг. Иймд CMOS элементийн оролтыг статик цэнэгт санамсаргүйгээр нэвт цохигдохоос хамгаалж резистор-диодоос тогтох 5.24-р зурагт үзүүлсэн хэлхээ бүхий хамгаалалтын хэлхээг ашигладаг. D1 диод нь нэмэх хүчдлийг VDD+0.7V-оор, D2 диод нь сөрөг хүчдлийг -0.7V-оор тус тус хязгаарлана.

Зураг 5.24. Оролтын хамгаалалтын хэлхээ

RCA-гаас анхлан гаргасан CMOS интеграл хэхээнүүд нь 4000А серийнх байв. Үүний дараа 4000А серийн өндөр хүчдлийн хувилбарууд болох буферлэгдсэн гаралттай 4000B болон буферлэгдээгүй гаралттай 4000UB сериүд гарч ирсэн.

Хүснэгт 5.9

4000B | 4000UB | |

Оролтын их хүчдэл VIH (I-input, H-high | ||

Тэжээлийн хүчдэл VDD=5V үед | 3.5V | 4.0V |

Тэжээлийн хүчдэл VDD=10V үед | 7.0V | 8.0V |

Тэжээлийн хүчдэл VDD=15V үед | 11.0V | 12.5V |

Оролтын бага хүчдэл VIL (I-input, L-low) | ||

Тэжээлийн хүчдэл VDD=5V үед | 1.5V | 1.0V |

Тэжээлийн хүчдэл VDD=10V үед | 3.0V | 2.0V |

Тэжээлийн хүчдэл VDD=15V үед | 4.0V | 2.5V |

Гаралтын их хүчдэл VOH (O-output, H-high) | ||

Тэжээлийн хүчдэл VDD=5V үед | 4.95V | |

Тэжээлийн хүчдэл VDD=10V үед | 9.95V | |

Тэжээлийн хүчдэл VDD=15V үед | 14.95V | |

Гаралтын бага хүчдэл VOL (O-output, L-low) | 0.05V | |

Оролтын их гүйдэл IIH (I-input, H-high) | 1.0µA | |

Оролтын бага гүйдэл IIL (I-input, L-low) | 1.0µA | |

Гаралтын их гүйдэл IOH (O-output, H-high) | ||

Тэжээлийн хүчдэл VDD=5V үед | 0.2mA | |

Тэжээлийн хүчдэл VDD=10V үед | 0.5mA | |

Тэжээлийн хүчдэл VDD=15V үед | 1.4mA | |

Гаралтын бага гүйдэл IOL (O-output, L-low) | ||

Тэжээлийн хүчдэл VDD=5V үед | 0.2mA | |

Тэжээлийн хүчдэл VDD=10V үед | 0.5mA | |

Тэжээлийн хүчдэл VDD=15V үед | 1.4mA | |

Саатлын хугацаа (propagation delay) | ||

Тэжээлийн хүчдэл VDD=5V үед | 150ns | 60ns |

Тэжээлийн хүчдэл VDD=10V үед | 65ns | 30ns |

Тэжээлийн хүчдэл VDD=15V үед | 50ns | 25ns |

Шуугианы өргөн (noise margin) | ||

Тэжээлийн хүчдэл VDD=5V үед | 1.0V | 0.5V |

Тэжээлийн хүчдэл VDD=10V үед | 2.0V | 1.0V |

Тэжээлийн хүчдэл VDD=15V үед | 2.5V | 1.5V |

Чадлын зарцуулалт (power dissipation) | 0.1mW (for f=100kHz) | |

Хамгийн их ажлын давтамж | 12MHz | |

74C сери нь CMOS элементийн хөлийг 74 серийн ТТЛ элементтэй адилхан болгосон хувилбар. Жишээ нь 2 оролттой 4 NAND бүхий 7400 ТТЛ элемент нь мөн 2 оролттой 4 NAND бүхий CMOS 74С00 элементтэй ерөнхийдөө адилхан бөгөөд түүний пакетынх нь хөлүүд ч адилхан давхцдаг гэж ойлгож болно.

74HC/HCT сери нь 74С-гийн сайжруулсан өндөр хурдтай хувилбарууд болно. Ингэхдээ гейтийн бүтцийг метал-оксид-хагас дамжуулагч бүтэцтэй байсныг хагас дамжуулагч-оксид-хагас дамжуулагч бүтэцтэй транзистораар сольсон тул эдгээрийг хагас дамжуулагч гейттэй бүлүүд ч гэж нэрлэдэг. 74HCT сери нь хөлнийх нь байрлалыг ТТЛ-тэй адилхан болгосон 74HC-ийн хувилбар болно.

74AC/ACT сери нь одоогоор CMOS-ийн хамгийн өндөр хурдтай, бага чадал зарцуулдаг хувилбарууд болно. 74ACT сери нь хөлнийх нь байрлалыг ТТЛ-тэй адилхан болгосон 74АС-ийн хувилбар болно.

Хүснэгт 5.10

4000B | 4000UB | |

Оролтын их хүчдэл VIH (I-input, H-high) | ||

Тэжээлийн хүчдэл VDD=5V үед | 3.5V | 4.0V |

Тэжээлийн хүчдэл VDD=10V үед | 7.0V | 8.0V |

Тэжээлийн хүчдэл VDD=15V үед | 11.0V | 12.5V |

Оролтын бага хүчдэл VIL (I-input, L-low) | ||

Тэжээлийн хүчдэл VDD=5V үед | 1.5V | 1.0V |

Тэжээлийн хүчдэл VDD=10V үед | 3.0V | 2.0V |

Тэжээлийн хүчдэл VDD=15V үед | 4.0V | 2.5V |

Гаралтын их хүчдэл VOH (O-output, H-high) | ||

Тэжээлийн хүчдэл VDD=5V үед | 4.95V | |

Тэжээлийн хүчдэл VDD=10V үед | 9.95V | |

Тэжээлийн хүчдэл VDD=15V үед | 14.95V | |

Гаралтын бага хүчдэл VOL (O-output, L-low) | 0.05V | |

Оролтын их гүйдэл IIH (I-input, H-high) | 1.0µA | |

Оролтын бага гүйдэл IIL (I-input, L-low) | 1.0µA | |

Гаралтын их гүйдэл IOH (O-output, H-high) | ||

Тэжээлийн хүчдэл VDD=5V үед | 0.2mA | |

Тэжээлийн хүчдэл VDD=10V үед | 0.5mA | |

Тэжээлийн хүчдэл VDD=15V үед | 1.4mA | |

Гаралтын бага гүйдэл IOL (O-output, L-low) | ||

Тэжээлийн хүчдэл VDD=5V үед | 0.2mA | |

Тэжээлийн хүчдэл VDD=10V үед | 0.5mA | |

Тэжээлийн хүчдэл VDD=15V үед | 1.4mA | |

Саатлын хугацаа (propagation delay) | ||

Тэжээлийн хүчдэл VDD=5V үед | 150ns | 60ns |

Тэжээлийн хүчдэл VDD=10V үед | 65ns | 30ns |

Тэжээлийн хүчдэл VDD=15V үед | 50ns | 25ns |

Шуугианы өргөн (noise margin) | ||

Тэжээлийн хүчдэл VDD=5V үед | 1.0V | 0.5V |

Тэжээлийн хүчдэл VDD=10V үед | 2.0V | 1.0V |

Тэжээлийн хүчдэл VDD=15V үед | 2.5V | 1.5V |

Чадлын зарцуулалт (power dissipation) | 0.1mW (for f=100kHz) | |

Хамгийн их ажлын давтамж | 12MHz | |